# General-Purpose Computing on Graphics Processing Units: GPU Processing of Protein Structure Comparisons

Todd Sullivan, Heather Nelson, Travis McBee, Mathew Alvino Mentor: Dr. Chi-Ren Shyu

CS 4970 – Senior Capstone Design I **Technical Report**Winter 2007

# **Table of Contents**

| L. | xecutive S | Summary                                     | 1  |

|----|------------|---------------------------------------------|----|

| 1  | Proble     | em Definition                               | 2  |

|    | 1.1 In     | ntroduction                                 | 2  |

|    | 1.1.1      | Needs Analysis                              | 2  |

|    | 1.1.2      | Market Analysis                             | 2  |

|    | 1.2 T      | echnical Background                         | 3  |

|    | 1.2.1      | Index-based Protein Substructure Alignments | 3  |

|    | 1.2.2      | General GPGPU Techniques                    | 4  |

|    | 1.2.3      | Current GPGPU Technologies                  | 6  |

|    | 1.2.3      | 3.1 Accelerator Performance                 | 7  |

|    | 1.2.3      | 3.2 BrookGPU Performance                    | 8  |

|    | 1.2.       | 3.3 Cg                                      | 10 |

|    | 1.2.4      | GPGPU Performance Techniques                | 10 |

|    | 1.2.       | 4.1 Cache-Efficient Memory Models           | 11 |

|    | 1.2.       | 4.2 Vertex Processor Code Motion Technique  | 11 |

|    | 1.2.       | 4.3 GPU Clustering                          | 13 |

|    | 1.3 G      | oals and Objectives                         | 14 |

|    | 1.4 O      | verall Approach                             | 15 |

|    | 1.4.1      | System Diagram                              | 17 |

|    | 1.4.2      | Advantages and Disadvantages                | 19 |

|    | 1.4.3      | Costs                                       | 19 |

| 2  | Requi      | rements Analysis                            | 20 |

|    | 2.1 S      | ystem Requirements and Constraints          | 20 |

|    | 2.1.1      | Operating Environment                       | 20 |

|    | 2.1.2      | Market Users and Characteristics            | 21 |

|    | 2.1.3      | Environmental Constraints                   | 22 |

|    | 2.1.       | 3.1 Quality and Reliability                 | 22 |

|    | 2.1.3      | 3.2 Human Factors                           | 22 |

|    | 2.1.4      | System Components                           | 24 |

|    | 2.1.5      | Software Interfaces and Libraries           | 24 |

|    | 2.1.6      | Communication Interfaces                    | 25 |

|    | 2.1.7      | Hardware Interfaces                         | 25 |

| 2.1.8 System Maintenance                       | 26 |

|------------------------------------------------|----|

| 2.2 Performance Requirements                   | 26 |

| 2.3 Resource Requirements                      | 27 |

| 2.3.1 Time                                     | 27 |

| 2.3.2 Resources                                | 28 |

| 2.3.3 Facilities                               | 28 |

| 2.3.4 Budget                                   | 28 |

| 2.4 Evaluation Metrics                         | 28 |

| 3 Design Specification                         | 29 |

| 3.1 Hardware                                   | 29 |

| 3.2 Data Requirements                          | 29 |

| 3.2.1 IPSA Data Sources                        | 29 |

| 3.2.2 Translation to a GPU Datatype            | 30 |

| 3.2.3 Matrix Translations                      | 30 |

| 3.2.4 Protein Chain Translations               | 32 |

| 3.3 Software                                   | 33 |

| 3.3.1 IPSA Profiler                            | 33 |

| 3.3.1.1 Class Diagram                          | 34 |

| 3.3.1.2 Data Flow Diagram                      | 35 |

| 3.3.2 Java-C++ Interaction                     | 36 |

| 3.3.2.1 High-Level Process Diagram             | 38 |

| 3.3.3 Alternative Java-C++ Interaction         | 39 |

| 3.3.3.1 Alternative High-Level Process Diagram | 39 |

| 3.3.3.2 Advantages and Disadvantages           | 40 |

| 3.3.4 The Compute_RMSD_D1 Function             | 40 |

| 3.3.4.1 Algorithm                              | 41 |

| 3.3.4.2 Eigenvalues and Eigenvectors           | 42 |

| 3.4 Testing Methods                            | 42 |

| 3.4.1 IPSA Profiler                            | 43 |

| 3.4.2 Java-C++ Interaction                     | 43 |

| 3.4.3 The Compute_RMSD_D1 Function             | 43 |

| 3.5 Scheduling and Task Assignments            | 44 |

| 4 | 4 System Implementation             | 46 |

|---|-------------------------------------|----|

|   | 4.1 GPGPU Limitations Demonstration | 46 |

|   | 4.1.1 2D Arrays versus 1D Arrays    | 46 |

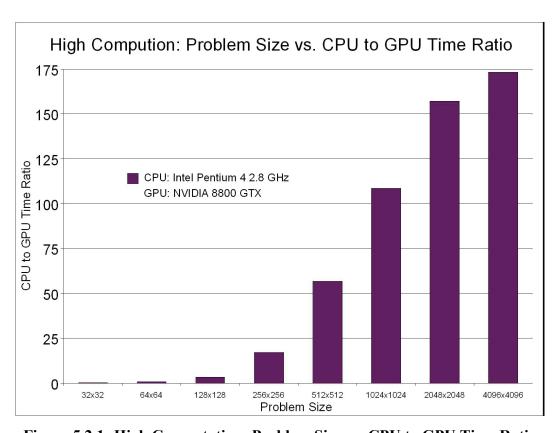

|   | 4.2 GPGPU Potential using Cg        | 47 |

|   | 4.2.1 Mathematical Computation      | 47 |

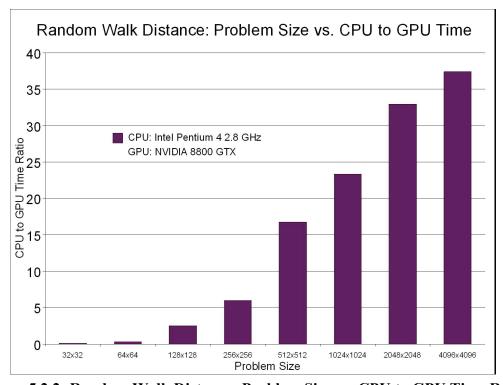

|   | 4.2.2 Average Random Walk Distance  | 49 |

|   | 4.3 IPSA                            |    |

|   | 4.3.1 IPSA Profiler                 | 52 |

|   | 4.3.2 Java-C++ Interaction          | 52 |

|   | 4.3.3 The Compute RMSD D1 Function  | 53 |

|   | 4.3.3.1 CPU Arrays to GPU Arrays    | 53 |

|   |                                     | 54 |

| 5 | 5 System Performance and Evaluation | 58 |

|   | 5.1 GPGPU Limitation Demonstrations | 58 |

|   | 5.1.1 2D Arrays versus 1D Arrays    | 58 |

|   | 5.2 GPGPU Potential using Cg        | 59 |

|   | 5.2.1 Mathematical Computation      | 60 |

|   | 5.2.2 Average Random Walk Distance  | 61 |

|   | 5.3 IPSA                            | 62 |

|   | 5.3.1 IPSA Profiler                 | 62 |

|   | 5.3.2 The Compute_RMSD_D1 Function  | 64 |

| 6 | 6 Summary and Conclusions           | 65 |

| 7 | 7 Future Work                       | 66 |

| 8 | 8 References                        | 67 |

## **Executive Summary**

The project's purpose is to learn about General Purpose Computing on Graphical Processing Units (GPGPU), determine the feasibility of porting an algorithm designed by a University of Missouri-Columbia PhD student, and develop prototypes that compute a portion of IPSA on the GPU and demonstrate using GPU-based computations within IPSA. The algorithm, known as Index-based Protein Substructure Alignment (IPSA), has an average response time of twenty minutes. Dr. Shyu hopes that the team's research into GPGPU technologies will show that GPU-based versions of his biology algorithms can perform faster than the current CPU versions and, in particular, that the GPU-based portion of IPSA is faster than its CPU counterpart.

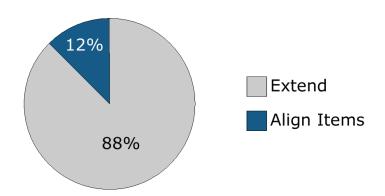

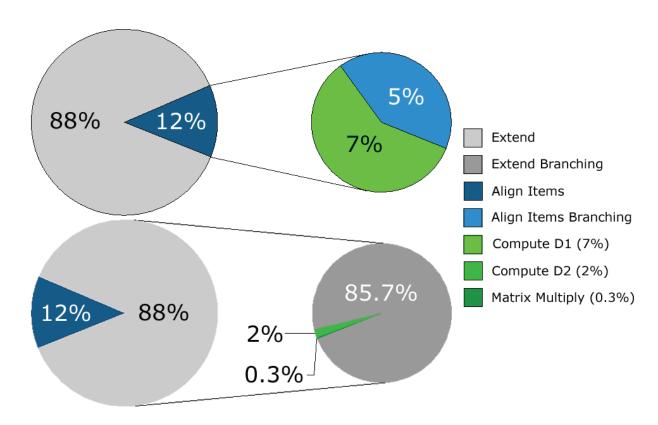

The team's study of GPGPU technologies and analysis of IPSA reveals that only 9.3% of IPSA's total processing time is parallelizable. The remaining 90.7% of the total processing time is consumed by sections with an abundance of branching and extensive nested looping, both of which are extremely slow on the GPU. Of the GPU-compatible 9.3%, the team created a GPU-based prototype of the Compute\_RMSD\_D1 function, which consumes 7% of the total processing time.

The GPU-based prototype calculates 102,400 chain comparisons simultaneously. The prototype is 9.828 times faster than the CPU-based computation. Without including any potential overhead from connecting the GPU-based computation with IPSA, the GPU-based IPSA algorithm is 1.076 times faster than IPSA and cuts 84 seconds off the total processing time. Any additional performance improvements require a redesign of IPSA that increases the amount of parallelizable code.

## **1 Problem Definition**

#### 1.1 Introduction

General-purpose computing on graphical processing units (GPGPU) is an emerging method for achieving high performance gains on various computing problems such as database operations, neural networks, and physics-based simulations. The higher number of cores and the more efficient processing of complex mathematical calculations on GPUs in comparison with CPUs makes GPGPU a fascinating new method for deploying algorithms. In an effort to reduce the runtime of protein-based search and retrieval algorithms, Dr. Chi-Ren Shyu of the University of Missouri-Columbia Medical Biological Digital Library Research Lab (MBDLRL) has asked the team to convert MBDLRL algorithms into comparable algorithms for processing on a GPU.

### 1.1.1 Needs Analysis

In particular, the team will study the potential for GPU-based MBDLRL algorithms and develop a prototype that implements a portion of PhD student Pin-Hao Chi's Index-based Protein Substructure Alignment algorithm (IPSA) [1] on the GPU. IPSA is part of the MBDLRL's Protein Database Search Engine project (ProteinDBS) [2]. The algorithm currently takes twenty minutes on average to complete one query. Dr. Shyu hopes that the team's research into GPGPU technologies will show that GPU-based MBDLRL algorithms can perform faster than the current CPU versions.

## 1.1.2 Market Analysis

The development of GPU versions of MBDLRL algorithms will benefit the study of proteins and various medical biology fields. Reducing processing time will allow ProteinDBS to service more queries. Protein retrievals, folding, and other algorithms will be more efficient and thus have a higher availability.

The experience the team will acquire and the framework that the team will develop is also applicable to many other research areas. Since GPGPU methods are still very new, the framework and documentation will provide a base for GPGPU applications in all computationally intensive research. Thus, the benefits of understanding GPGPU methods and developing a solid framework for converting algorithms to run on the GPU will have benefits beyond the protein retrieval algorithm that the team will study. In fact, InformationWeek chose the field of GPGPU as one of the five disruptive technologies to watch in 2007 [3].

### 1.2 Technical Background

The technical background includes Index-based Protein Substructure Alignments [1], general GPGPU techniques [4], current GPGPU technologies, and GPGPU performance techniques.

## 1.2.1 Index-based Protein Substructure Alignments

Through the use of computer algorithms, biologists have the ability to solve many computationally challenging problems. For example, one area of interest in molecular biology surrounds protein structure matching. Proteins, the essential building blocks of organisms, fold into complicated three-dimensional structures. Each structure has a unique shape that often determines its biological function. IPSA presents a fast structure retrieval system to find similar proteins in a database of over 40,000 elements [5]. With such a large dataset, speed often becomes an issue since biologists need to have access to a system that provides results in real time. As such, IPSA achieves much higher efficiency than its well-recognized competitors, DALI and CE. IPSA is 37.66 times faster than DALI and 2.78 times faster than CE.

Although IPSA performs structure retrieval much faster than many other available systems, the algorithm could benefit from additional increases in speed. By looking at overall

structure and important substructure elements, such as the commonly occurring alpha helix and beta sheet, the system can achieve higher accuracy than its predecessor, ProteinDBS. However, an average response time of twenty minutes places a burden on the system and proves an inconvenience to researchers. The project team will examine the data structures and algorithms used to determine how they may be processed using a GPU in order to increase efficiency.

IPSA features many large data structures that facilitate fast protein structure retrieval.

Each protein is considered as a sequence of terms. The algorithm maps substructure representatives into an M-tree. Then, an inverted-protein index organizes the terms associated with a protein by considering topology constraints. Using this database, the system can easily map query proteins to other similar structures. The team could potentially achieve an increase in speed simply by moving IPSA's large data structures such as the M-tree and inverted-protein onto the GPU. The team outlines areas with GPU-based computation potential in Section 5.3.1.

## 1.2.2 General GPGPU Techniques

Modern day GPUs specialize in performing large floating-point matrix arithmetic in small amounts of time. Much of the power of the GPU has evolved due to the switch from hardwired pipelines to programmable components. For example, the NVIDIA GeForce FX replaced register combiners with programmable pixel shaders. GPUs also specialize in parallel processing, and it is because of this specialization that they are so effective in GPGPU. For example, modern GPUs can compute 330 billion floating-point operations per second. However GPGPU is not the best choice for many algorithms in their original form. Many of these algorithms have to be reworked or have a translator made to function on a GPU. [6]

GPGPU techniques must follow the stream programming model to make use of the parallelism within GPUs. GPGPU applications implement several basic operations of the stream

programming model. These operations are map, reduce, scatter and gather, scan, stream filtering, sort, and search.

Map and reduce are two simple operations. Map is essentially applying a function to a given set of data elements. For example, if one has a stream of data in the range [0.0, 1.0), then a map operation can convert the values into the range [0, 255] by multiplying each element by 256 and then taking the floor of the result.

Reduce computes a smaller stream from a larger stream. An example application of reduce is when calculating the largest element from a dataset. A fragment program reads two values and writes the largest one to the pass' result buffer. The process continues in parallel until the stream contains only one element, which is the dataset's maximum.

Scatter and gather are read and write operations that access memory indirectly. Scatter is the operation for assigning a value to an element of an array. Gather is the process of retrieving an array element's value. Gather is implemented on a GPU by fetching a pixel from a texture using specific texture coordinates. Due to the design of GPU hardware, a fragment program cannot implement scatter. Instead, developers use several tricks to implement scatter such as rewriting the problem in terms of gather or using the vertex processor for scatter operations.

The scan and stream filtering operations are also helpful tools. Given an operator + and an array of n elements  $[a_0, a_1, ..., a_{n-1}]$ , scan returns the array  $[a_0, (a_0 + a_1), ..., (a_0 + a_1 + ... + a_{n-1})]$ . The stream filtering operation selects a subset of the overall dataset and only processes on the subset. This technique is useful for simple data partitioning and collision detection.

Sorting operations are difficult to implement on fragment processors in current GPUs since GPU hardware does not implement scatter and data-dependent operations are difficult to implement in parallel processors. Thus, all GPU-based sorting is impartial to the input data.

Many sorting operations are significantly faster on the GPU than on the CPU. For example, PBSN, a cache-efficient GPU-based sorting network algorithm, is almost six times faster than the CPU-based Qsort available in the Intel compiler.

Searching operations on the GPU are not able to beat CPU algorithms in terms of reducing the processing time of a single search. Instead, the parallelism of the GPU allows developers to increase throughput by processing multiple searches at the same time. Most basic searching algorithms such as binary search are possible on the GPU, but algorithms that are more complex require specialized GPU data structures.

### 1.2.3 Current GPGPU Technologies

The base technologies for converting algorithms to run on the GPU are the OpenGL Shading Language (GLSL) [7], DirectX [8], and Cg [9]. RapidMind [10] and PeakStream [11] both offer commercial products for deploying high-performance applications on a variety of processors including CPUs, GPUs, and the Cell, while NVIDIA is developing a technology called CUDA [12] that is specifically for GPGPU. Other languages and extensions that are available include Sh [13], Shallows [14], Accelerator [15], and BrookGPU [16].

GLSL, DirectX, and Cg are all APIs and toolkits for writing graphics programs. These APIs are the base for programming on popular video cards made by ATI and NVIDIA. GLSL is an open standard while DirectX is a proprietary Microsoft product and Cg is a proprietary NVIDIA product. Even though Cg is proprietary, its compiler supports OpenGL's standards and thus can create programs that run on both ATI and NVIDIA video cards. The basis for using GLSL, DirectX, or Cg for GPGPU is that one can hijack the graphics processing pipeline and force the GPU to perform other tasks instead of rendering graphics. All other languages,

extensions, and commercial products convert code into GLSL or DirectX methods during the compilation process.

RapidMind and PeakStream both offer commercial products for taking advantage of various types of processors. RapidMind is comprised of the former developers of Sh. Both companies provide APIs for C++. Unfortunately, the products are too costly for the project. For example, PeakStream's API costs \$1,000 per GPU on an academic server and \$295 per user on an academic workstation.

NVIDIA's CUDA technology is a new technology that enables standard C programming on a GPU. The technology supports both Linux and Windows XP operating systems and includes native multi-GPU support. While CUDA appears to be the most promising technology for future GPGPU applications, the technology is currently in closed testing and is not available for this project.

Sh and Shallows are C++ libraries that in simplest terms provide a high-level API above GLSL that allows developers to spend less time with the GLSL-specific programming details. Accelerator and BrookGPU are both toolkits for taking advantage of GPU processing power without requiring developers to learn GPU specific APIs or programming languages. The team is interested in the applicability of Accelerator and BrookGPU to the project because both technologies significantly reduce the time required to create GPU programs.

#### 1.2.3.1 Accelerator Performance

Accelerator is a library for C# that provides a high level API for performing data parallelism operations. [15] includes a performance evaluation between C# using Accelerator, handwritten Pixel Shader 3.0 assembly code, and CPU-based C++ code. The evaluation benchmarks ten operations: sum, matrix-vector multiplication, matrix-matrix multiplication, life,

demosaic, convolve, rotate, corner detection, motion estimation, and stereo matching. Overall, the Accelerator code performs within 50% of the speeds of the handwritten Pixel Shader code. The Accelerator code performs better than the CPU-based C++ code on seven out of the ten operations, but when the Accelerator code performs worse, it performs significantly worse.

Accelerator's slow processing is from many design decisions. Accelerator uses just-in-time compilation for its fragment processor programs. This means that the library compiles each fragment processor program at runtime, when the fragment program is needed. Even though the library caches these programs for later use, the just-in-time compilation overhead and the library's other execution costs take up 9% of the running time on average.

Accelerator's worst performance was in the rotate and motion estimation operations. These operations involve many gather operations with special out-of-bounds access cases.

While GPUs have hardware support for gather, the DirectX C# API does not provide access to the hardware support. Thus, Accelerator cannot utilize the GPU's resources while handwritten Pixel Shader code has access to this hardware support.

While Accelerator is typically faster than the CPU-based C++ code, it is not as fast as handwritten Pixel Shader 3.0 code. Additionally, Accelerator in only available for C#, and thus requires a Windows machine running DirectX and the .Net Framework. For these reasons, the team will not use Accelerator for the project.

#### 1.2.3.2 BrookGPU Performance

BrookGPU extends C to include stream processing constructs that use the GPU to perform calculations. BrookGPU includes a compiler and a runtime environment that allows Brook programs to run on both ATI and NVIDIA GPUs with either OpenGL or DirectX. Brook virtualizes two important stream computing aspects. OpenGL, DirectX, and Cg limit the number

of outputs from a fragment program and limit stream dimensions and size. BrookGPU virtualizes these aspects and, for example, allows users to create streams that are not bound by texture memory restrictions within the GPU.

BrookGPU provides a high-level abstraction of the graphics pipeline through offering streams and kernels. Streams are analogous to textures within GPU memory, but they do not have limits on their size. Kernels are analogous to fragment programs that execute on fragment processors within the GPU. The main difference between kernels and fragment programs is that BrookGPU kernels allow for an arbitrary amount of output streams while fragment programs have a limit on the number of outputs and the size of textures used.

[16] includes a performance evaluation of BrookGPU. On average, BrookGPU's DirectX output is within 80% of hand-coded GPU implementation performance. BrookGPU's OpenGL output is significantly less efficient. Most of these inefficiency issues are due to the hand-coded GPU implementations using problem-specific knowledge to find "shortcuts." These optimizations are not possible when using BrookGPU.

BrookGPU is significantly faster than Accelerator. When using the DirectX runtime, BrookGPU is only marginally slower than hand-coded GPU implementations. Additionally, BrookGPU's abstraction will allow the team to port a larger portion of the IPSA algorithm to the GPU within the limited timeframe for the project. Due to BrookGPU's significant decrease in programming time in comparison with using the base technologies of OpenGL, DirectX, or Cg, the team will use BrookGPU for porting applicable portions of IPSA to the GPU.

#### 1.2.3.3 Cg

In order to reach the goals outlined in Section 1.3, the project group must choose a language that demonstrates the raw power of the GPU for high computation and computational biology problems in a short period of time. As such, Cg presents a programming language using C-like syntax and philosophy [9]. Each member of the group has worked extensively with the C language and will feel comfortable learning a similar language. In fact, one of the main reasons that the designers of Cg chose to implement an environment similar to C was to provide ease of programming to developers since they would feel familiar with the language.

Other goals met by the designers of Cg fit well with the project's purpose to perform computation on a GPU, contrary to the hardware's intended purpose. Since Cg implements a C-like interface, it is hardware-oriented while being general purpose [9]. The designers provided full support for hardware programming, similar to an assembler language, so that the developers could have more power. Therefore, the project group will have complete control over the underlying elements and will be able to demonstrate the best performance that GPGPU techniques can achieve for selected computationally intensive problems.

### 1.2.4 GPGPU Performance Techniques

GPGPU developers can use several techniques for improving program performance. Most of these techniques require direct programming with OpenGL, DirectX, or Cg. Three examples of GPGPU performance techniques are cache-efficient memory models, the vertex processor code motion technique, and GPU clustering.

#### 1.2.4.1 Cache-Efficient Memory Models

Through the use of an intuitive and flexible language, successful GPU computation requires the effective representation of data in memory. Many applications beyond graphics can benefit from parallel GPU processing, including database indexes. These types of programs benefit since they can be expressed independently, and the GPU is able to process the same function on multiple elements of a two dimensional array. As shown by the model in [17], efficient algorithms achieve a two to five times improvement versus a CPU. Therefore, if researchers ignore the design of the hardware, they will not achieve much increase in speed since the GPU is intended for maximum efficiency through independent, simultaneous computation.

In order to maintain high throughput, one must develop a system that reduces that number of cache misses. Looking up elements that do not currently reside in the cache creates a high overhead. Therefore, [17] presents a technique that decomposes the input into smaller blocks, called quads. The GPU processes these separately so that a smaller dataset resides in memory. Then, a rendering pass performed at each stage reduces the dataset to its final return value. The project group will use the decomposition technique to reduce IPSA's protein chains into smaller pieces that the GPU can most efficiently process. By following an effective memory model, the project group expects to achieve a two to five times speedup on the GPU-based portions of IPSA in relation to their original CPU-based counterparts.

#### **1.2.4.2** Vertex Processor Code Motion Technique

[18] includes the vertex processor code motion technique for improving the efficiency of GPGPU programs. The technique focuses on the fact that GPUs include both vertex processors (VPs) and fragment processors (FPs), but GPGPU programs typically only use fragment processors. By offloading appropriate instructions to the VPs, [18] was able to reduce execution

time of a Gaussian filter program by 40% and reduce the FP workload in ten of eighteen GPGPU programs tested.

Data in the GPU pipeline flows from VPs to rasterization and interpolation to FPs. The key to moving instructions from FPs to VPs is to identify movable instructions. [18] defined movable instructions as instructions that are executable, accessible, equivalent, and independent.

An instruction is executable if the VP instruction set includes it. For example, the txld instruction is not executable because it is not within the VP instruction set since VPs cannot read textures. Additionally, instructions are accessible if the VP registers can replace the registers used on the FPs. For example, registers on a VP cannot replace sampler registers on FPs because samplers involve textures and VPs cannot operate on textures.

An instruction is equivalent if the instruction is linear and does not use lower precision registers on the VP for high-precision data. Since FPs receive linearly interpolated data from VPs, one can only move linear operations to VPs. If an operation is not linear, then the rasterization and interpolation process between VPs and FPs in the GPU pipeline with mangle the data. Additionally, one cannot use lower precision registers within VPs to pass high-precision data to FPs because this will result in rounding errors.

An instruction is independent if it does not depend upon any unmovable instruction above it in the fragment program. For example, if an instruction  $I_1$  is dependent upon a previous instruction that is not movable, then  $I_1$  is not movable. This restriction is obvious because the previous instruction must execute before  $I_1$  and moving  $I_1$  to VPs will cause it to execute before the instruction that it depends upon.

[18] found that their technique of moving instructions from FPs to VPs improved the performance of ten out of eighteen GPGPU programs tested. The technique did not work for all

programs because offloading work from FPs to VPs increases the amount of data passed between the two. During this passing of data from VPs to FPs within the GPU pipeline, the rasterization and interpolation process became the bottleneck of some of the applications. While the technique can certainly increase efficiency of GPGPU programs, implementing the technique requires extensive knowledge of GPU programming. Thus, the team will not attempt this technique during the project.

#### 1.2.4.3 **GPU Clustering**

[19] discusses the design, implementation, and results of using the Lattice Boltzmann Model (LBM) for flow simulation on a GPU cluster. The GPU cluster uses 32 nodes that are connected by a 1 Gigabit Ethernet switch. Each node has two Pentium Xeon 2.4GHz processors, 2.5GB of memory, and one GeForce FX 5800 Ultra with 128MB of memory. The GPU cluster executed each step of the simulation 4.6 times faster than [19]'s CPU cluster implementation.

[19] first developed an LBM algorithm on a single GPU. The algorithm ran 8 times faster on the GeForce FX 5900 Ultra when compared to their CPU version running on a Pentium IV 2.53GHz. One can easily visualize the design of the LBM used for the single GPU algorithm as a rectangle in three dimensions.

When scaling the LBM onto the GPU cluster, [19] roughly split the domain into cubes. Each node processes one cube. The data along the borders of each cube have to pass to neighboring GPUs for computation. This introduced a bottleneck while transferring data from a node's GPU to its CPU, and then across the network.

The primary challenge for [19] was minimizing the cost of communication between nodes. [19]'s cluster was hindered by using an AGP 8x bus, which only has a peak upstream of 133 MB/sec. They were also hindered by the fact that each GPU only had 128 MB of memory.

According to the team's test results, between 24 to 28 nodes was optimal. With more than 28 nodes the performance dropped significantly due to network collisions and other issues. In an effort to combat the network issues, the team set up a scheduling routine that made sure that not all of the nodes were transmitting border data at the same time.

Overall, [19] concluded that the price per performance of their GPU cluster was significantly better than purchasing a comparable CPU cluster. Today, with the performance increases in GPUs such as significantly more GPU memory and processing cores, the performance of [19]'s GPU cluster would only be greater. While a GPU cluster is not within the budget for the project, the promise of GPU clusters is certainly interesting.

## 1.3 Goals and Objectives

The team's ultimate goal is to port the most promising portion of IPSA into a working GPU-based prototype that performs at least twice as fast as its CPU-based counterpart. The ultimate goal of the project is certainly lofty, especially considering that none of the team members has any experience working with GPUs. Since the team is lacking in general experience with GPUs, the team must meet many preliminary learning, discovery, and testing goals before the team attempts to tackle the final goal.

First, the team will review the GPU programming tutorials in [20] and [21]. These tutorials demonstrate the basic concepts of using graphics processing pipeline to perform nongraphics related tasks. All of the tutorials that the team will review use Cg to complete the GPU programming tasks. After completing the tutorials, the team will produce GPGPU programs that demonstrate the best performance possible for select GPU-based algorithms barring hand-writing Pixel Shader 3.0 assembly code. These GPGPU case study programs are the deliverables of this first phase.

Next, the team will examine the BrookGPU example code and explanations in [16]. The team will learn to write simple GPU-based programs that implement general GPGPU techniques such as map and reduce. The GPGPU programs that demonstrate map and reduce are the deliverables for the second phase.

Once all team members have a grasp of GPGPU techniques and BrookGPU programming, the team will begin analyzing the feasibility of porting IPSA to the GPU. This will include a thorough study of the algorithm so that all team members understand the processing steps and data structures involved. During this third phase, the team will develop a profiling program, which will analyze the runtime spent in each section of IPSA and determine the most lucrative portions of IPSA for porting to the GPU.

During the final phase of the project, the team will implement on the GPU the portion of IPSA that has the most promise for parallelized processing. The team will also develop a prototype that demonstrates how the IPSA algorithm could transfer and receive data from the GPGPU program. The final deliverables of the project are the GPU-based program that implements a portion of IPSA and the IPSA-GPU interaction program that demonstrates how IPSA will access the GPU.

## 1.4 Overall Approach

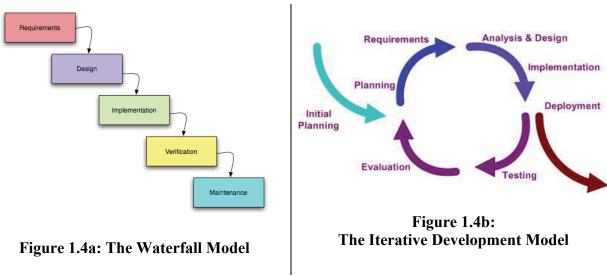

The team will follow the waterfall model for the project. Since the project consists of porting a portion of an existing, well-defined algorithm to run on a GPU, the waterfall model is the best choice for a development model. After completing the initial learning and discovery goals listed under the Goals and Objectives section, the team will follow the general waterfall process model as shown in Figure 1.4a.

In addition to the waterfall model, the team will use a version of the iterative development model as shown in Figure 1.4b for determining the best possible translation of IPSA 's data structures into comparable data structures for the GPU and for determining the best fragment programs for performing the GPU computations. This process will include many design, implementation, and evaluation phases as the team refines the data structure and fragment program designs to achieve maximum performance. Since the design of the data structures is one of the most important issues to consider with GPGPU methods, this iterative development will be a large portion of the project.

Graphics taken from Wikipedia.com under the Creative Commons Attribution ShareAlike License v. 2.5.

The team will use Cg and BrookGPU for developing the project's GPU-based programs.

This decision is based on recommendations from Robert Luke and Derek Anderson, both graduate students that have experience porting algorithms to the GPU. The development, testing, and production environment includes two different graphics cards: an NVIDIA 8800 GTX with

128 processing cores and 768 MB of memory and an ATI x800 XT PE with 16 processing cores and 256 MB of memory.

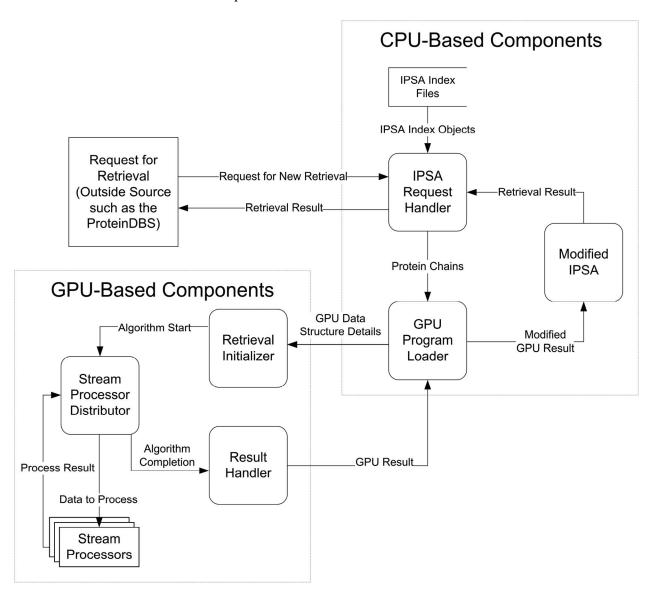

### 1.4.1 System Diagram

The program will include many modules as detailed in Figure 1.4.1. An outside source such as an existing program within ProteinDBS will request to run the protein retrieval algorithm with a given set of parameters. The IPSA Request Handler, a component running on the CPU that is a modified version of the program that the original IPSA developer created, will receive the request and ultimately return the result. The IPSA Request Handler will load the nine IPSA index files and send the proteins to process to the GPU Program Loader. The GPU Program Loader will create the necessary data structures on the motherboard memory and load the GPU program onto the GPU.

Once the data is loaded onto the GPU, the goal of the GPU program is to execute the algorithm while minimizing the amount of references to non-GPU memory or procedures. The Retrieval Initializer will generate the GPU data structures that correspond to the CPU data structures created earlier. Once initialization of the memory is complete, the Stream Process Distributor will begin executing the algorithm.

The Stream Process Distributor executes the kernel programs that run on each data point in the GPU's memory. The component sends the datasets to be processed to the stream processors (pixel shaders) on the GPU. Each of these stream processors produces results that the Stream Processor Distributor receives and aggregates accordingly.

Once the stream processing is complete, the Result Handler component on the GPU sends the GPU Program Loader the result. The GPU Program Loader stores the result in the motherboard memory and sends the GPU result to the modified IPSA algorithm. The modified

IPSA algorithm executes the CPU-based IPSA algorithm while using the results that the GPU produced for the specific calculations that the team ported to the GPU. Once the Modified IPSA component sends the IPSA Request Handler the final result, the IPSA Request Handler sends the result to the outside source that requested the retrieval.

Figure 1.4.1: The Component Diagram

### 1.4.2 Advantages and Disadvantages

The advantage of the above component layout is that the layout ensures that the GPU-based algorithm minimizes its interaction with the CPU and motherboard memory. The key to gaining a speedup is to reduce the amount of GPU-CPU interaction. One needs to design the system to run on the GPU for the highest possible percentage of overall processing time.

The main disadvantage to the team's approach is the difficulty in coordinating efficient data structures between the GPU and CPU memory. This disadvantage is acceptable because it is currently the only way to use GPUs for general purpose computing. Since GPUs cannot store objects and data in the same way as CPU and motherboard memory, one must create a translation between the two representations. This translation and choice of data representation on the GPU is critical to the efficiency of GPU-based algorithms.

#### 1.4.3 **Costs**

The most obvious costs of the project are the costs of the hardware. An NVIDIA 8800 GTX alone currently costs 575 dollars while an ATI x800 XT PE costs 250 dollars [22]. The hardware costs are definitely expensive for a college student, but Dr. Shyu's budget can sufficiently handle the cost. Section 2.3 presents a more thorough cost analysis.

## 2 Requirements Analysis

## 2.1 System Requirements and Constraints

The system has many requirements and constraints including required hardware, quality and reliability requirements, human factors, required software libraries, and performance requirements. While all constraints are important, the human factors in Section 2.1.3.2 had the largest impact on the project's timeline and goals. The time requirements in Section 2.3.1 were also significantly affected by the human factor constraints.

### 2.1.1 Operating Environment

The team will use two development machines as detailed in Table 2.1.1. The team will use multiple development machines in order to alleviate the human-based constraints described in Section 2.1.3.2 and to meet the project goals in the limited time span. Dr. Shyu provided Computer 1 while Todd Sullivan, one of the team members, provided Computer 2. Since both video cards support OpenGL and DirectX and both operating systems provide proper drivers for their respective video cards, the Cg and BrookGPU programs will execute correctly on both machines.

|                  | Computer 1              | Computer 2        |

|------------------|-------------------------|-------------------|

| Video Card       | NVIDIA 8800 GTX         | ATI x800 XT PE    |

| Processing Cores | 128                     | 16                |

| GPU Memory       | 768 MB                  | 256 MB            |

| CPU              | Intel Pentium 4 2.8 GHz | AMD64 3400+       |

| CPU Memory       | 4 GB DDR400             | 3 GB DDR400       |

| Operating System | Fedora Core 6 (Linux)   | Windows XP/Cygwin |

**Table 2.1.1: The Development Machines**

As described in Section 1.2.3.2, BrookGPU's DirectX runtime is significantly faster than its OpenGL runtime. While this does not affect the development phase of the project, the restriction certainly affects the performance of the BrookGPU programs. Due to time and budget

constraints, the team cannot install a Windows operating system on Computer 1. Instead, the team has to use a free Linux distribution, which does not provide DirectX. Thus, in a real-world BrookGPU-based IPSA program, Dr. Shyu should run the program in a Windows environment in order to achieve maximum performance.

While BrookGPU's DirectX runtime is faster than its OpenGL runtime, working in Windows comes with its costs. In order to take advantage of widely available Linux libraries and other tools, the team must compile and execute the BrookGPU program using Cygwin, a Linux-like environment for Windows. As a result, in order to achieve the performance gain from the BrookGPU DirectX runtime, the team must manage working in an entwined Windows/quasi-Linux environment.

The team will not need to manage any web servers or database environments. IPSA's data structures are stored as nine index files. Each index file is a serialized Java object. IPSA's own algorithms and tools maintain its database. The team's GPU-based program will need to access IPSA's data structures, but the program will not need to alter them in any fashion. Thus, the team can access IPSA's local database by calling methods in Java in a similar fashion to Java's built-in data structures such as Vector and TreeMap.

#### 2.1.2 Market Users and Characteristics

In compliance with U.S. regulations, the team will not violate any patents held by other GPGPU researchers and companies. The tools that the team will use for the project, such as Cg and BrookGPU, do not impose any regulatory or license-based restraints on the project. Sections 1.1.1 and 1.1.2 describe the project's market demand and customer requirements respectively.

#### 2.1.3 Environmental Constraints

In order to satisfy customer requirements, the team must address quality and reliability constraints. Due to the nature of the system, the GPU-based program meets suitability and safety requirements because they are built into the original IPSA algorithm and, provided the GPU-based program is a direct port of portions of IPSA, are not actual requirements for the project. The team must also accommodate many human factors that are uncontrollable and sometimes unpredictable. The majority of these human factors reduce the time available for analyzing IPSA, designing the GPU-based solution, and implementing the prototype.

### 2.1.3.1 Quality and Reliability

The GPU-based solution must reliably provide similar results in comparison with the original algorithm. The original IPSA algorithm, written in Java, uses double precision floating point numbers. Current video cards use single precision floating point numbers. Due to this constraint, the GPU-based computations will offer less precision than the original CPU-based computations. This constraint is unavoidable in current hardware. The team hopes that since all computations will be less precise, the resulting values will remain the same in relation to each other. Since the resulting values will remain the same relative to each other, the ranking scheme will still return the same result.

#### 2.1.3.2 Human Factors

Human factors severely reduced the amount of time available for the third and fourth phases of the project as described in Section 1.3. The team did not receive the IPSA source code until April 2. Upon receipt of the algorithm, the team did not receive the algorithm's dataset until April 6. The source code contained no inline comments and no documentation explaining the process of compiling and executing the various IPSA modules.

Additionally, the source code did not initially compile correctly because the team lacked several required libraries and the source code had multiple locations of hard-coded, system-specific paths. These library dependencies and hard-coded paths were not disclosed in any documentation and IPSA's original creator did not remember all of the locations where paths were hard-coded. As a result of these issues, the team was not able to successfully compile and execute IPSA until April 11.

Aside from human factors pertaining to source code issues, the team did not receive the primary development machine, Computer 1, until April 2. The machine had Red Hat Linux preinstalled, which was partially corrupted and unusable. Thus, the team spent a few days trying to fix the system. Once the proposition of fixing the system became futile, the team reformatted Computer 1's hard drive, installed Fedora Core 6, and installed all of the required libraries as detailed in Section 2.1.5. The primary development machine was functional on April 5.

Due to these human factors, the team had approximately two and a half weeks to profile IPSA, choose a suitable section to port to the GPU, and develop the prototype. The team remained steadfast (to no avail) in requesting the required source code, dataset, and development machine prior to the delivery of the items. To counter these human factors, the team spent the time before delivery of the items learning to program in Cg and BrookGPU and completing the first and second phases of the project's goals as described in Section 1.3. The team also countered these limiting factors through time management that allowed the team members to dedicate significant portions of each day to the project during the two-week period before the project's presentation at the Advisory Board.

### 2.1.4 System Components

The primary system components are the IPSA index files, the Java-based IPSA programs, and the GPU-based program that the team will develop. The team will develop a modified version of the Java-based IPSA algorithm that demonstrates how to use the GPU-based program for performing select calculations. The team will not manipulate the IPSA index files. Instead, the team will access the indexes through the Java-based IPSA program.

#### 2.1.5 Software Interfaces and Libraries

The team will use Cg and BrookGPU to develop the deliverables described in Section 1.3. These libraries require OpenGL or DirectX to run. As covered in Section 2.1.1, both development machines contain support in hardware and software for OpenGL, while Computer 2 contains support for DirectX. When using OpenGL, the Cg and BrookGPU programs also both require GLUT, the OpenGL Utility Toolkit, and GLEW, the OpenGL Extension Wrangler.

Since the IPSA algorithm is written in Java, the team will use a modern Java Virtual Machine for Java 1.5 to execute the IPSA algorithm. Java includes constructs such as the Runtime.exec() method for executing operating system-specific commands. The team will use Runtime.exec() to execute and control the GPU-based program from within Java.

Since this method uses commands specific to the machine's operating system, the team will have to use different commands for invoking the GPU-based program on a Linux machine versus a Windows machine. The primary difference is that in Windows the team will have to use Runtime.exec() to load a new Cygwin instance and then load and control the GPU-based program from within the Cygwin process. On a Linux machine the team will simply use Runtime.exec() to load and control the GPU-based program directly.

#### 2.1.6 Communication Interfaces

The team will manage the communication between the Java-based program and the GPU-based program using the features of the Process object in Java. After loading the GPU-based program using the Runtime.exec() method in Java, the team will control the GPU-based program by using the process' standard input and output streams. Java's Process object allows the team to read from the GPU-based program's standard output and write to its standard input as if the GPU program is running in a console and the Java program is the keyboard and screen.

Cg and BrookGPU manage the communication interface between the CPU processes and the GPU processes. Additionally, the IPSA programs manage the communication channels responsible for receiving retrieval requests and returning results. Thus, the team has little oversight responsibilities and abilities in regards to these communication interfaces.

#### 2.1.7 Hardware Interfaces

Table 2.1.1 details the hardware for each development system. The only notable interface for the project is the connection between the video card and the CPU in each machine. Computer 1 contains a PCI Express 1.0 bus that connections the 8800 video card with the CPU. Computer 2 uses an AGP 8x bus for connecting the x800 video card with the CPU. The PCI Express 1.0 bus has a maximum data rate of 4 GB/s while an AGP 8x bus has a maximum data rate of 2.1 GB/s. While these constraints limit the maximum performance that the GPU programs can achieve, they do not affect the design or development details of the GPU-based programs.

### 2.1.8 System Maintenance

The team must provide full documentation for compiling and executing the deliverables outlined in Section 1.3. Since none of the team members will be available after the project's completion, the documentation must provide enough information for a new team to continue the research with as few relearning periods as possible. In order to maintain the system, the administrator will either need prior experience with GPGPU or be willing to learn GPGPU techniques. The team strongly recommends that any maintenance staff at least have experience with graphics programming using OpenGL or DirectX.

## 2.2 Performance Requirements

The portion of IPSA that the team ports to the GPU must execute faster than performing the calculations on the CPU. The definition of "faster" is important because the GPU cannot outperform the CPU when executing simple calculations on small vectors or matrices. For example, the GPU performs significantly worse in comparison to the CPU when performing calculations on three-by-three matrices because the GPU is designed to process large quantities of data at the same time. Thus, determining which is "faster" by having each program perform one protein chain comparison at a time will always result in the CPU-based program being faster.

In order to take advantage of the GPU, the GPU-based program should pack thousands of three-by-three matrices into a single matrix. Instead of performing the calculation on one three-by-three matrix at a time, the GPU-based program should calculate all of the results simultaneously. The team should then compare the time elapsed for this bulk processing with the average time from the CPU-based program's sequential processing of an equal number of three-by-three matrices. Thus, the pertinent performance requirement is that the GPU-based

program processes all of the protein chains in bulk faster than the original CPU-based section of code processes the protein chains sequentially.

## 2.3 Resource Requirements

The human factors significantly affected the time requirements for the project. The team also required many important resources in Section 2.3.2, such as Computer 2, because of the environmental constraints. The project's facilities were fairly small for the team size, but the accommodations were paid for by other projects and thus acceptable.

#### 2.3.1 Time

As described in Section 2.1.3.2, Human Factors, time management is crucial for adapting to unpredictable events. Each team member averaged eight hours per week over a ten-week development period, totaling 320 work hours. At an average hourly rate of fifty dollars per hour, the time costs are \$16,000, as detailed in Table 2.3.4.

Due to the environmental constraints in Section 2.1.3, each team member did not consistently work eight hours each week. Instead, the team's work hours included a sharp, sustained rise during the three and a half weeks at the beginning of April. In fact, over the weekend of April 21<sup>st</sup> and 22<sup>nd</sup> two team members practiced Extreme Programming [23] and each clocked two twelve to fourteen hour work days in a row. These irregular work patterns were necessary to accommodate the unavoidable constraints described in Section 2.1.3.2 and were achieved by early planning that eliminated other obligations of each team member during the heavy development period.

#### 2.3.2 Resources

Aside from the IPSA source code and protein dataset, the only resources required are the development machines detailed in Table 2.1.1. Computer 1's video card cost \$575 while its other parts total \$1,200. Computer 2's video card cost \$250 while its other parts total \$950. The total resource costs are \$2,975, but an important note is that most of the development machines' parts were reused parts from other projects.

#### 2.3.3 Facilities

The team requires at least one location where team members can operate both development machines side-by-side. Dr. Shyu's student cubicle space meets this requirement. The project does not incur additional expenses from using the cubicle space because the particular cubicle is not in use by another project and Dr. Shyu's other projects pay for the costs of the space.

## **2.3.4 Budget**

| Employment | \$16,000 |

|------------|----------|

| Computer 1 | \$1,775  |

| Computer 2 | \$1,200  |

| Total      | \$18,975 |

**Table 2.3.4: The Cumulative Project Budget**

### 2.4 Evaluation Metrics

The project's evaluation metrics are the production of the deliverables described in Section 1.3 and a performance evaluation of the GPU-based IPSA Compute\_RMSD\_D1 function that shows that the function is faster than its CPU-based counterpart. Section 2.2 includes the project's definition of the term "faster" and describes how the team will assess the GPU-based program's performance in comparison with the CPU-based calculations. The process is a complete success if the team produces the deliverables and positive performance evaluation.

## 3 Design Specification

The majority of the project's design process centers around designing data structures and designing software modules. Since IPSA includes its own data structures, the data structure designs involve translating IPSA's data structures into GPU-compatible data. The software, on the other hand, involves modifying IPSA's program flow to include GPU computations and designing software for profiling IPSA and for performing the GPU-based calculations.

### 3.1 Hardware

The project does not require any specialized hardware designs, which allowed the team to focus primarily on software designs. While the team did not create any hardware designs, the project requires knowledge of the GPU pipeline and the general design of video cards. Section 1.2 discusses this general GPU design.

## 3.2 Data Requirements

IPSA requires many different data sources as described in Section 3.2.1. The team's GPU-based computations involve one particular data structure – a protein chain consisting of an array of doubles. Sections 3.2.2 and 3.2.3 describe translating these protein chains into GPU-compatible data.

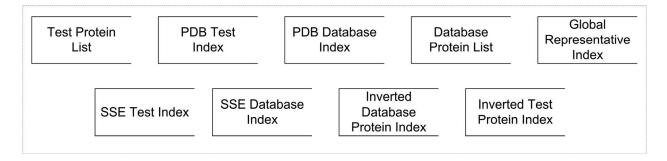

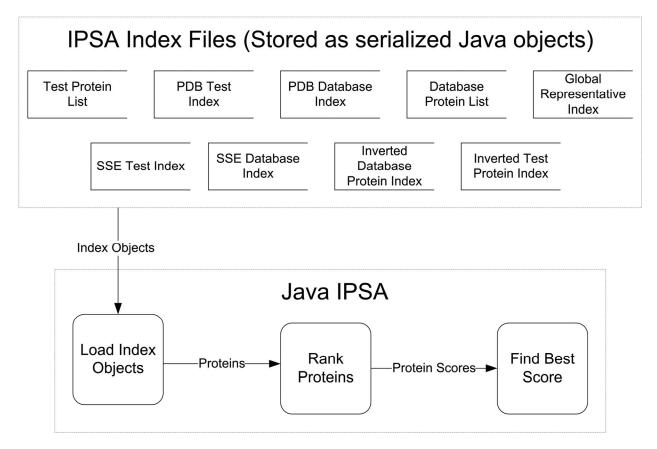

#### 3.2.1 IPSA Data Sources

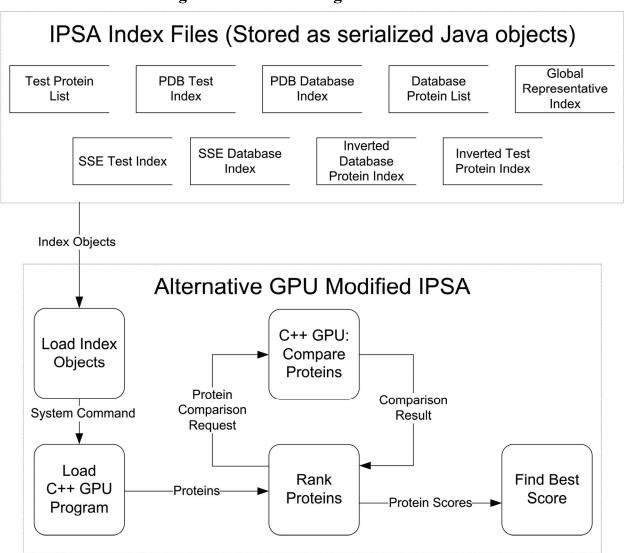

The IPSA algorithm includes nine data files as shown in Figure 3.2.1. These nine data files include two protein lists and seven indexes. IPSA stores these data structures as serialized Java objects. The project's goals do not require the team to alter these data structures in any way. Instead, the team only has to access the proteins in the data structures using method calls similar to Java's built-in Vector and TreeMap classes.

Figure 3.2.1: IPSA Data Sources

### 3.2.2 Translation to a GPU Datatype

In order to process the proteins on the GPU, the team must translate the protein's structure in Java into a suitable structure in GPU memory. IPSA stores the protein chains as arrays of doubles (double precision floating point numbers) that are either thirty or forty-five elements long. Since current GPUs can only process floats (single precision floating point numbers), the protein chains will lose half of their precision in GPU memory.

Additionally, GPUs store four floats at each pixel on a texture. These four floats are for the red, green, blue, and alpha values of the pixel. Thus, each element of an array on the GPU is considered a float4, which can be thought of as a C struct with floats denoted by pixel.r, pixel.g, pixel.b, and pixel.a. Since IPSA calculates most chain values in groups of three, the GPU arrays use the red, green, and blue floats while disregarding the alpha float.

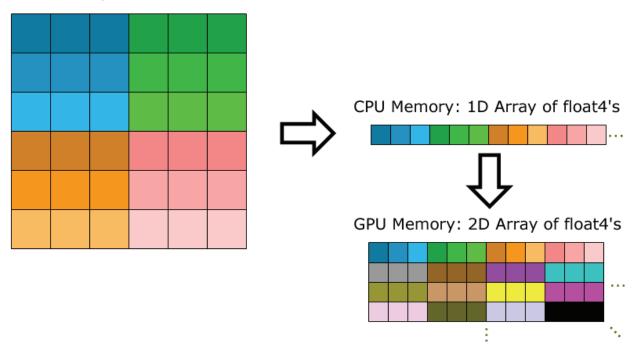

#### 3.2.3 Matrix Translations

When performing comparisons on chains, IPSA uses many three-by-three matrices. Since the GPU's main skill is performing calculations in bulk, the GPU-based algorithm needs to pack many three-by-three matrices into a single giant matrix. Figure 3.2.3 demonstrates this process of storing many three-by-three matrices as a single texture on the GPU.

Float Array of 3x3 Matrices

Figure 3.2.3: Three-by-Three Matrix Translation

First, the three-by-three matrices are placed in a larger square matrix with sides that are a multiple of three. Second, each row of each three-by-three matrix is then placed into a single float4 with the float4s red value storing the row's first element, green value storing the row's second element, and blue value storing the row's third element. These float4s are arranged in CPU memory as a one-dimensional array of float4s.

Figure 3.2.3 demonstrates this second step as the first arrow in the center of the figure. The top row of the blue three-by-three matrix collapses into the first float4 element in the 1D array. Similarly, each three-by-three row collapses into the single element in the 1D array that contains the same color as the original row of floats.

After creating a one-dimensional array of float4s in CPU memory, the array is written to a texture in GPU memory as shown by the second array in Figure 3.2.3. While writing the array

to a texture in GPU memory, the one-dimensional array wraps around into a two-dimensional texture. The resulting 2D texture is three times as long as it is high.

For clarity, Figure 3.2.3 demonstrates the process with a two-by-two matrix of three-by-three matrices. In reality, the second step (first arrow in the figure) writes the first row of three-by-three matrices before moving to the second row. Thus, on a larger set of three-by-three matrices the matrix denoted by orange is not placed next to the matrix denoted by green.

#### 3.2.4 Protein Chain Translations

Since the GPU needs to compute many protein chain comparisons at once, the GPU also needs to pack protein chains into a single large texture. As stated earlier, protein chains are either thirty or forty-five floats long. Thus, each protein chain requires either ten or fifteen float4s where each float4 contains three floats in the RGB values.

For efficiency reasons, the large texture containing these chains needs to store each chain as a symmetric matrix of float4s. The smallest symmetric matrix that contains at least fifteen elements is a four-by-four. Figure 3.2.4 shows how multiple protein chains map into the large texture.

Figure 3.2.4: Protein Chain Mapping into Texture

The colored blocks in Figure 3.2.4 denote float4s of the texture that each chain occupies. The white blocks are float4 elements that contain all zeroes and are necessary wasted space. The blue, green, and orange chains are thirty floats long. The last chain is forty-five floats long. Each thirty-float chain wastes six float4s while each forty-five-float chain wastes one float4.

#### 3.3 Software

The project's software designs include the IPSA Profiler, Java-C++ Interaction, and the Compute\_RMSD\_D1 function. The IPSA Profiler and Java-C++ Interaction programs will integrate into the original IPSA program. The Compute\_RMSD\_D1 function is a GPU-based program that is a translation of IPSA's Compute\_RMSD\_D1 function.

## 3.3.1 IPSA Profiler

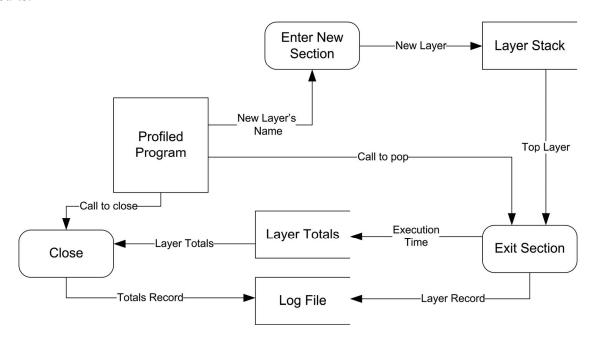

The IPSA Profiler's purpose is to provide a convenient method for recording the processing time of each section of IPSA and analyzing the results. While analyzing a program, the profiler maintains a stack of each layer of executing code. The layer on the top of the stack is the current, most narrow section of code that is executing in the program.

When entering a new section of the program, the profiler places a new layer on the top of the stack. The profiler records the new layer's start time, depth, and layer number when adding the layer to the stack. When exiting a section of the program, the profiler pops off the layer at the top of the stack. The profiler records the popped layer's end time and writes the layer's information to the current session's log file. The profiler also maintains execution time totals for each layer in relation to its name and its path.

Once the program completes execution, the profiler sends the log file to an analyzer that generates a summary report of the profile. The analyzer creates a plain-text report that displays total time by layer, percent total time by layer, total time by layer with respect to its path, and

percent total time by layer with respect to its path. The analyzer sorts these values so that the report clearly shows the sections of the program that consume the majority of the execution time.

# 3.3.1.1 Class Diagram

The IPSA Profiler contains three classes as shown in Figure 3.3.1.1. The Profiler class and ProfileAnalysis class are public classes. The Layer class is an internal class of the Profiler class.

When entering a new section of a program, the program calls the Profiler class' push method. When exiting a section of a program, the program calls the Profiler class' pop method. The Profiler class' close method writes the final profile to disk.

| Profiler                                              | Layer              | ProfileAnalysis                           |

|-------------------------------------------------------|--------------------|-------------------------------------------|

| -layers : Stack <layer></layer>                       | +name : String     | -max_name_length : Int                    |

| -layer_counter : Int                                  | +basename : String | +processBaseName(in path : String)        |

| -out : PrintStream                                    | +ID : Int          | +processPathName(in path : String)        |

| -totals_with_path : Map <string,layer></string,layer> | +start_time : Long | +process(in path : String)                |

| -totals_basename : Map <string,layer></string,layer>  |                    | -outputEntryRuntimes(in entries : Vector) |

| +push(in layer_name : String)                         |                    | -outputEntryPercents(in entries : Vector) |

| +pop()                                                |                    |                                           |

| +close()                                              |                    |                                           |

Figure 3.3.1.1: IPSA Profiler Class Diagram

# 3.3.1.2 Data Flow Diagram

Figure 3.3.1.2 illustrates the activity of an instance of the Profiler class when profiling a program. The actions correspond to the previous English language description of the IPSA Profiler. The Profile Analysis class does not need to a data flow diagram because the process simply involves parsing a text file, calculating percents, sorting the results, and output the sorted results.

Figure 3.3.1.2: IPSA Profiler Data Flow Diagram

#### 3.3.2 Java-C++ Interaction

Figure 3.3.2 illustrates the control flow of the original IPSA algorithm. The program loads the index objects from disk as serialized Java objects, sends the proteins to a Rank Proteins procedure, and then sends the protein scores to a Find Best Score procedure. The Find Best Score procedure sorts the scores in descending order and outputs the results.

Figure 3.3.2: Java-C++ Interaction High-Level Process Diagram

IPSA's designer implemented the algorithm in Java. Regardless of the library or method used for GPGPU, the GPU-based program is ultimately a C++ application. In order to integrate the two, the Java program needs to start and control the C++ application.

The Java program starts the C++ program by executing an operating system-specific command and attaching the new process to a Process object. The Java program then extracts the input and output streams from the Process object. The Java program uses the output stream in a

similar way to a human using keyboard input to a command line program. The Java program uses the input stream to read data from the C++ program.

When the C++ program reads from its standard input, it reads commands sent to it by the Java program through the Process object's output stream. Similarly, when the C++ program writes to its standard output, it writes data to the Process object's input stream. This process is similar to connecting programs together using sockets. The difference is that neither program has to know anything about sockets and the C++ program is completely oblivious to who controls it. Thus, when testing developers can execute the C++ program from the command line and provide input using the keyboard.

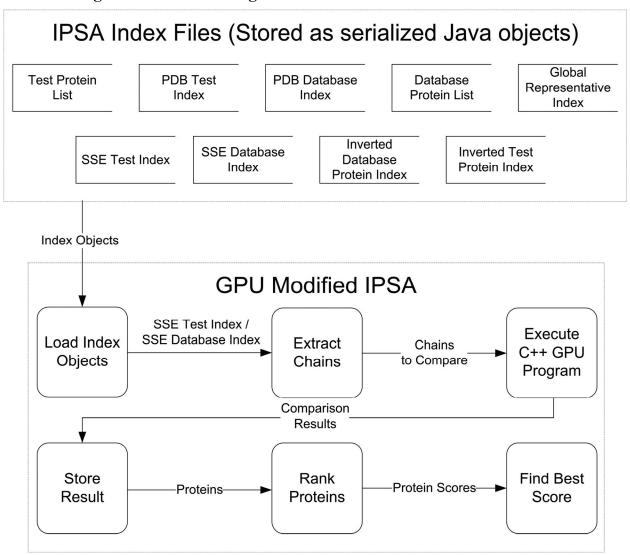

Once the Java program starts the C++ program, it provides the C++ program with the list of protein chains to compare. The C++ program simultaneously computes all of the comparisons. Once the computations are complete, the C++ program sends the results to the Java program. The Java program stores all of the results and begins the normal IPSA algorithm. Whenever the Java program's execution reaches a computation that the C++ program calculated, the Java program retrieves the result from memory instead of computing the result with the CPU.

# 3.3.2.1 High-Level Process Diagram

Figure 3.3.2.3: Java-C++ Interaction High-Level Process Diagram

## 3.3.3 Alternative Java-C++ Interaction

Alternatively, the Java program could send a protein chain comparison request to the C++ program when the Java program needs the comparison result. The two programs would communicate in the same way, but instead of bulk processing the comparisons in the beginning of the algorithm, the C++ program would process each comparison as they are needed. Figure 3.3.3.1 depicts this alternative design.

### 3.3.3.1 Alternative High-Level Process Diagram

Figure 3.3.3.1: Alternative Java-C++ Interaction High-Level Process Diagram

#### 3.3.3.2 Advantages and Disadvantages

The primary disadvantage to the original Java-C++ interaction design in Figure 3.3.2.3 is the high memory usage. While the C++ program is calculating protein comparisons, the C++ program and the Java program both have all of the protein chains stored in memory. Once the C++ program finishes calculating the comparisons, the Java program stores the results in memory for the entire duration of the IPSA algorithm.

The alternative design eliminates this memory usage issue because the C++ program only stores the two proteins that it is currently comparing. Additionally, the Java program does not store all of the results in memory for the entire algorithm. Instead, the Java program only stores one comparison result at any point in time.

Unfortunately, the alternative design does not take advantage of the GPU's ability to calculate thousands of protein comparisons simultaneously. While requiring less memory, the alternative design has significant performance issues. Thus, the higher memory usage of the original design is necessary to take advantage of the GPU's bulk computation ability.

# 3.3.4 The Compute\_RMSD\_D1 Function

Section 5.3.1 describes the results of profiling IPSA with the IPSA Profiler. The results of the profiling clearly show that the Compute\_RMSD\_D1 function within IPSA has the most potential for GPU-based computation. The Compute\_RMSD\_D1 function performs a comparison on two protein chains. Each protein chain is either thirty or forty-five floats long. The algorithm produces many intermediate three-by-three matrices during the process. The result is a single float.

#### 3.3.4.1 Algorithm

The following bullets and pseudo code describe the Compute\_RMSD\_D1 algorithm. The input chains that the algorithm compares are denoted by chain8 and chain9. All of the calculations are matrix calculations. Most of the calculations perform computations on three different lines of the matrices at the same time. The pseudo code is a broad generalization of the actual process for one comparison. The GPU-based version of the algorithm must adapt each computation to work on a two dimensional array containing thousands of comparisons that are computed simultaneously.

1) Calculate the mean of each chain

```

mean8 = Sum( chain8 ) / Size( chain8 );

mean9 = Sum( chain9 ) / Size( chain9 );

```

2) Shift each chain's floats by its corresponding mean values.

```

PointsOf( chain8 ) = PointsOf( chain8 ) - mean8;

PointsOf( chain9 ) = PointsOf( chain9 ) - mean9;

```

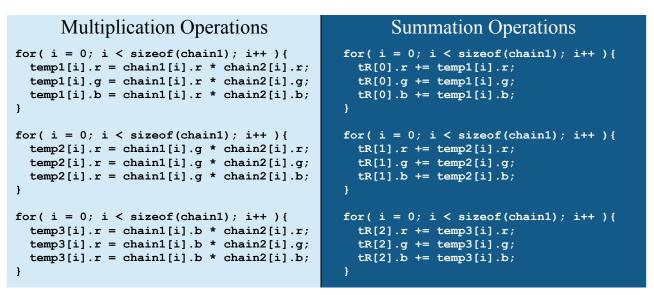

3) Calculate a three-by-three matrix *tR*.

```

Row1(tR) = Sum(PointsThatAreMultiplesOfThree(chain8) * chain9);

Row2(tR) = Sum(PointsThatAreMultiplesOfThreePlus1(chain8) * chain9);

Row3(tR) = Sum(PointsThatAreMultiplesOfThreePlus2(chain8) * chain9);

```

4) Transpose *tR* into *R*.

```

R = Transpose(tR);

```

5) Calculate the three-by-three matrix tR \* R.

```

tRR = MatrixMultiply(tR, R);

```

6) Calculate the eigenvalues mu and eigenvectors a of the tR \* R matrix.

```

mu = GetEigenvalues( tRR );

a = GetEigenvectors( tRR );

```

7) Calculate and normalize the *b* vectors.

```

b = Sum( R * ColumnsOf( a ) ) / SquareRoot( mu );

```

8) Calculate the rotation matrix tU using the b vectors and the eigenvectors a.

```

tU = ColumnMultiply(b, a);

```

9) Transpose tU into U.

```

U = Transpose(tU);

```

10) Calculate the root mean square error.

```

tempchain = Sum( ColumnsOf( chain9 ) * Columns of U );

rms = Sum( Square( chain8 - tempchain ) );

```

11) Return the root mean square deviation.

```

rmsd = SquareRoot( rms / chain_size );

```

## 3.3.4.2 Eigenvalues and Eigenvectors

Step 6 in Section 3.3.4.1 involves calculating eigenvalues and eigenvectors. The process of computationally determining a matrix's eigenvalues and eigenvectors is complicated. This process requires more time than the project's constraints allow. Thus, the GPU-based prototype does not calculate the eigenvalues or eigenvectors. To ensure the accuracy of the output, the team will hardcode these values while testing the program. To ensure an accurate performance evaluation, the team will remove the eigenvalue and eigenvector computation time from the execution time of the CPU-based algorithm as described in Section 5.3.2.

# 3.4 Testing Methods

The team will use comparisons between program output and either hand-determined correct output or output from the original IPSA program to determine whether each piece of software is working correctly. The IPSA Profiler and Java-C++ Interaction will use hand-determined output. The Compute\_RMSD\_D1 function will naturally use the output from the original IPSA function.

#### 3.4.1 IPSA Profiler

The team will test the accuracy of the IPSA Profiler by running the profiler on a program that simply contains multiple nested layers that each cause the execution thread to sleep for a predefined number of seconds. Since each layer sleeps for a predefined number of seconds, the team can hand calculate a report that summarizes the execution time at each layer and along each execution branch. The team will compare the hand-calculated report with the report that the profiler generates. If the reports are the same, then the IPSA Profiler does not have any bugs and works properly.

#### 3.4.2 Java-C++ Interaction

The team will test the Java-C++ interaction by using a predefined list of protein chain comparisons and comparison results. The Java program will send the list of protein chain comparisons to the C++ program. The C++ program will match each protein chain comparison with its predefined comparison result and send the comparison results back to the Java program. The Java program will output the results to the console. If the results are the same as the hand-calculated results then the Java-C++ interaction works correctly.

# 3.4.3 The Compute\_RMSD\_D1 Function

The team will test the GPU-based Compute\_RMSD\_D1 function by outputting to the console the result of each step described in Section 3.3.4.1. The team will compare these results with the corresponding results from the original Java function. If all of the results are the same, then the GPU-based function calculates the values correctly for a single protein chain comparison.

Since the GPU-based function calculates thousands of comparisons at the same time, the team needs to determine if all of the comparisons are calculated correctly. To do this, the team

will write the textures to CPU memory after each step described in Section 3.3.4.1 and then output to the console selected results from the matrix of results. The team will compare these results with the corresponding results from the original Java function.

# 3.5 Scheduling and Task Assignments

Table 3.5a: Schedule ID Task Name Start Finish Duration 2/4 2/11 2/18 2/25 3/11 3/18 3/25 4/8 4/15 4/22 4/29 Form Group 2/5/2007 2/9/2007 **Determine Project** 2/12/2007 2/16/2007 Problem Statement 2/23/2007 3/6/2007 1.5w 3/7/2007 Literary Review 3/16/2007 1.5w 3/16/2007 Combine PS's and LR's 3/22/2007 1w 2/16/2007 Explore How GPGPU Works 3/1/2007 2w 2/23/2007 3/9/2007 Study CG, BrookGPU, other options. 2.2w BrookGPU Case Studies 3/9/2007 3/30/2007 3.2w Cg Case Studies 3/19/2007 4/17/2007 4.4w **IPSA Profiler** 4/2/2007 4/6/2007 1w Program IPSA Segments with GPGPU 4/9/2007 4/24/2007 2.4w 4/16/2007 4/23/2007 1.2w Prepare Presentation Prepare Final Report 3/22/2007 5/23/2007 9w

| Table 3.5b: Task Assignments            |          |          |          |          |  |  |

|-----------------------------------------|----------|----------|----------|----------|--|--|

|                                         | Mathew   | Travis   | Heather  | Todd     |  |  |

|                                         | Alvino   | McBee    | Nelson   | Sullivan |  |  |

| Problem Statement                       |          |          |          |          |  |  |

| Writing                                 | •        | •        | •        | •        |  |  |

| Editing                                 | <b>•</b> | •        | •        | •        |  |  |

| D :                                     | 1        |          |          |          |  |  |

| Requirements Analysis                   |          | •        |          | •        |  |  |

| Writing                                 | •        | *        | •        | *        |  |  |

| Editing                                 |          | •        | •        | •        |  |  |

| Design Specification                    |          |          |          |          |  |  |

| Designs                                 |          |          | •        | •        |  |  |

| Writing                                 |          |          | •        | •        |  |  |

| Editing                                 |          |          | •        | •        |  |  |

|                                         | 1        |          |          |          |  |  |

| System Implementation                   |          |          |          |          |  |  |

| 2D Arrays versus 1D Arrays              |          |          |          | •        |  |  |

| Cg Mathematical Computation             |          | •        | •        |          |  |  |

| Cg Average Random Walk Distance         |          |          | •        |          |  |  |

| IPSA Profiler                           |          |          |          | •        |  |  |

| IPSA Java-C++ Interaction               |          |          |          | *        |  |  |

| IPSA Compute_RMSD_D1 Function           |          |          | •        | *        |  |  |

| Writing                                 |          |          | •        | •        |  |  |

| Editing                                 |          |          | •        | •        |  |  |

| System Performance and Evaluation       |          |          |          |          |  |  |

| 2D Arrays vs. 1D Arrays Data Collection | •        |          |          | •        |  |  |

| Cg Mathematical Computation             | •        |          | •        | •        |  |  |

| Data Collection                         |          |          | •        |          |  |  |

| Cg Average Random Walk Distance         |          |          |          |          |  |  |

| Data Collection                         |          |          | •        |          |  |  |

| IPSA Compute_RMSD_D1 Function           |          |          |          | •        |  |  |

| Data Collection                         |          |          |          |          |  |  |

| Writing                                 |          |          | •        | •        |  |  |

| Editing                                 |          |          | •        | •        |  |  |

| Summary and Canalysians                 | ]        |          |          |          |  |  |

| Summary and Conclusions                 |          | <u> </u> |          |          |  |  |

| Writing Editing                         |          | •        |          |          |  |  |

| Editing                                 |          |          |          | •        |  |  |

| Future Work                             |          |          |          |          |  |  |

| Writing                                 | •        |          | •        | •        |  |  |

| Editing                                 | •        |          | <b>•</b> | •        |  |  |

|                                         |          |          |          |          |  |  |

| Advisory Board Presentation             |          |          |          |          |  |  |

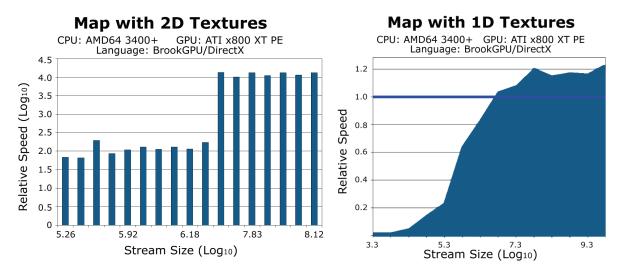

| Presentation Creation                   | •        | •        | <b>•</b> | •        |  |  |